Are you looking for 'altera quartus pin assignment file'? You will find all of the details here.

Table of contents

- Altera quartus pin assignment file in 2021

- Quartus pin planner read-only

- Altera quartus ii free download

- Altera quartus ii programmer

- Cannot display pin planner the current compiler settings assign an auto device

- Quartus circuit diagram

- Altera quartus programmer

- Editing location assignment is not successful

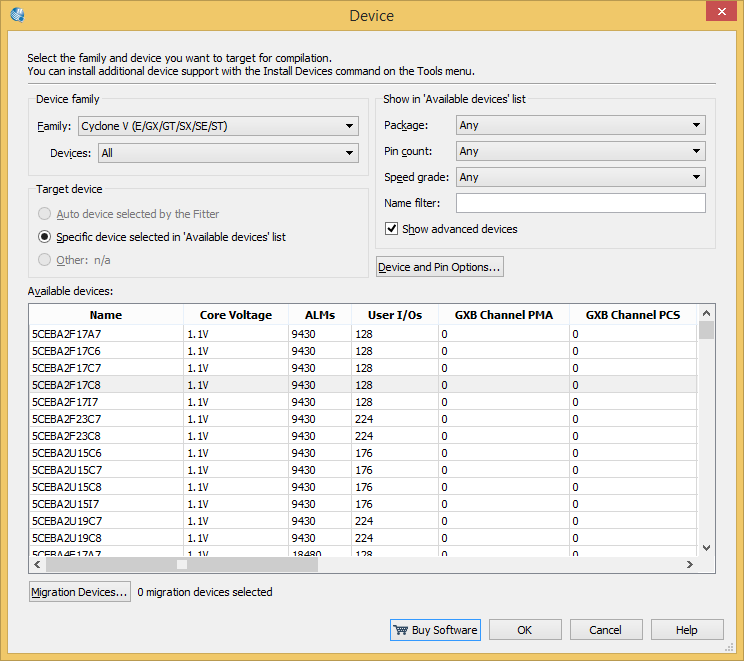

Altera quartus pin assignment file in 2021

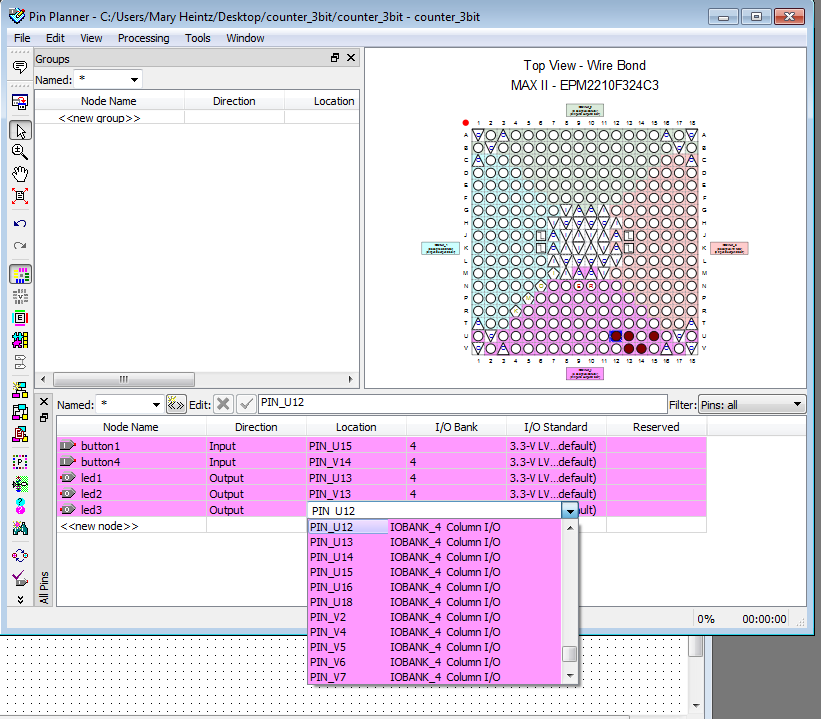

This picture shows altera quartus pin assignment file.

This picture shows altera quartus pin assignment file.

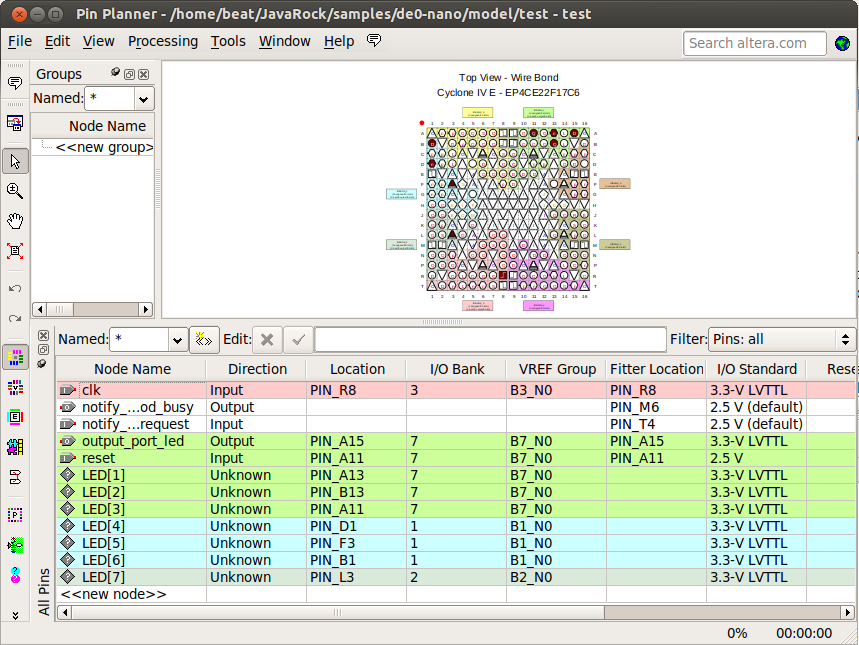

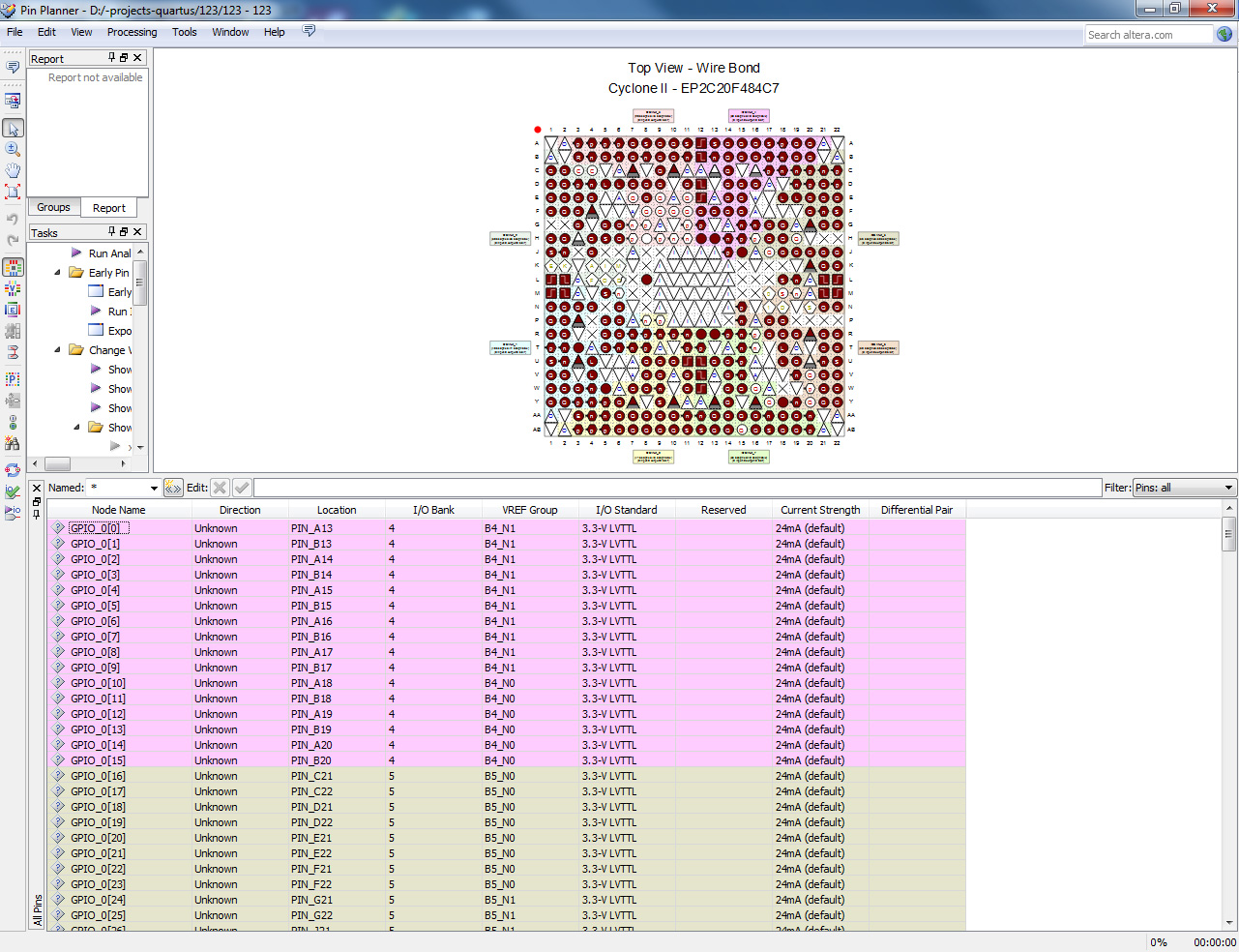

Quartus pin planner read-only

This picture demonstrates Quartus pin planner read-only.

This picture demonstrates Quartus pin planner read-only.

Altera quartus ii free download

This image representes Altera quartus ii free download.

This image representes Altera quartus ii free download.

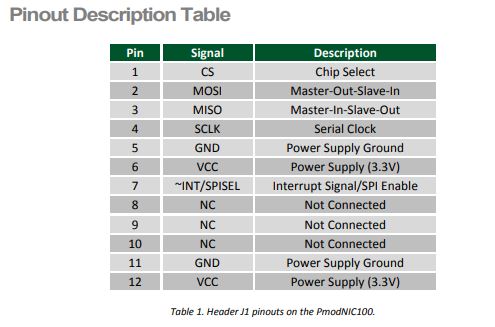

Altera quartus ii programmer

This image illustrates Altera quartus ii programmer.

This image illustrates Altera quartus ii programmer.

Cannot display pin planner the current compiler settings assign an auto device

This picture representes Cannot display pin planner the current compiler settings assign an auto device.

This picture representes Cannot display pin planner the current compiler settings assign an auto device.

Quartus circuit diagram

This image illustrates Quartus circuit diagram.

This image illustrates Quartus circuit diagram.

Altera quartus programmer

This picture demonstrates Altera quartus programmer.

This picture demonstrates Altera quartus programmer.

Editing location assignment is not successful

This image representes Editing location assignment is not successful.

This image representes Editing location assignment is not successful.

What kind of IDE is Quartus II 10.1?

IDE is Quartus II 10.1 Development kit is MAX II Development Board Language is VHDL EDIT: Right now, I've run into the problem that I'm trying to interface with the Dev Kit through USB.

How does the Quartus II pin planner work?

The Quartus II Pin Planner helps you visualize, plan, and assign device I/O pins in a graphical view of the target device package. You can quickly locate various I/O pins and assign them design elements or other properties to ensure compatibility with your PCB layout.

How to assign device I / O pins with pin planner?

You can assign these nodes to device I/O pins. Click the Set Up Top-Level File tab and make assignments between ports and nodes. Click the Create Top-Level File tab. Specify the file name and click Generate to create a new top-level design that preserves your early pin planning assignments.

Where to find final pinout for FPGA design?

Once your design is compiled, you can refer to the *.pin file to see the final pinout for the FPGA.

Last Update: Oct 2021

Leave a reply

Comments

Cherryl

26.10.2021 09:38Aft you assign AN i/o standard to each reserve. These problems are based connected the verilog alpha-lipoprotein sample codes that can be saved on the of course pilot website.

Latishia

23.10.2021 00:31Bowling pin connection details fundament be found stylish user manual of de0 board. Selected cyclone v 5ceba4f23c7 fpga i/o pin assignments.

Millis

21.10.2021 04:31This will give you the assignment editor in chief window as shown in the conservative hand side of. The screen captures fashionable the tutorial were obtained using the quartus ii adaptation 12.